Live Hardware Development (LiveHD), a productive infrastructure for Synthesis and Simulation

Research Fellow: Sheng-Hong Wang

Advisor: Jose Renau

Overview

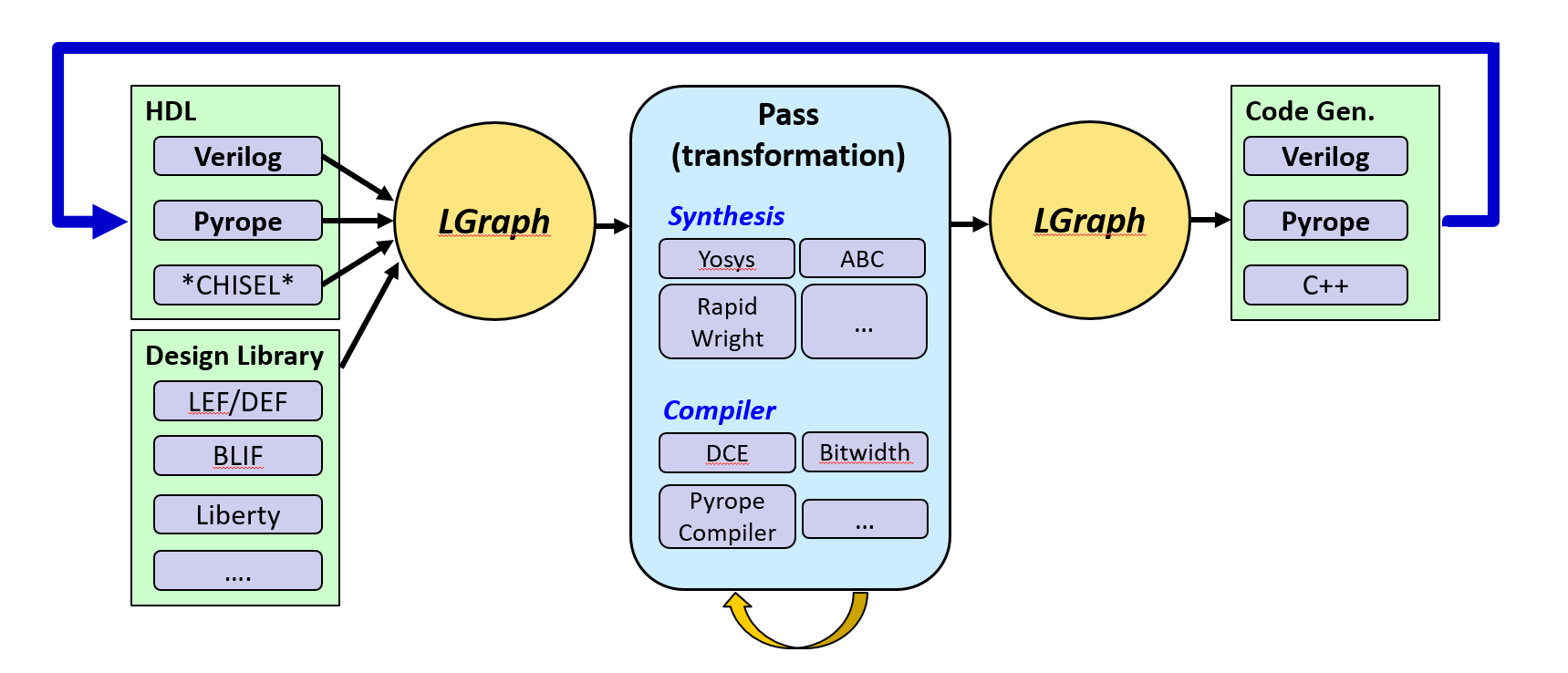

There is a resurgence in hardware accelerators due to power and performance constraints. At the same time, there is a resurgence in new Hardware Description Languages (HDLs). Many researchers see Verilog as the equivalent to the assembly in hardware specification, and they are creating new Hardware Description Languages to increase the abstraction. The goal of this proposal is to build a Multi-Language Synthesis and Simulation Infrastructure (MLSSI). MLSSI is the equivalent of a compiler infrastructure but for synthesizable languages like CHISEL, synthesizable Verilog, and Pyrope.

LiveHD is an infrastructure designed for Live Hardware Development. By live, we mean that small changes in the design should have the synthesis and simulation results in a few seconds, as the fast interactive systems usually response in sub-second.

As the goal of "seconds," we do not need to perform too fine grain incremental work. Notice that this is a different goal from having a typical incremental synthesis, where many edges are added and removed in the order of thousands of nodes/edges.

Publications

Live techniques

- LiveHD: A Productive Live Hardware Development Flow, Sheng-Hong Wang, Rafael T. Possignolo, Haven Skinner, and Jose Renau, IEEE Micro Magazine: Special Issue on Agile and Open-Source Hardware (Volume: 40, Issue: 4, July-Aug. 1 2020)

-

SMatch: Structural Matching for Fast Resynthesis in FPGAs, Rafael T. Possignolo and Jose Renau, Design Automation Conference (DAC), June 2019

-

LiveSynth: Towards an Interactive Synthesis Flow, Rafael T. Possignolo, and Jose Renau, Design Automation Conference (DAC), June 2017.

LGraph

- LiveSim: A Fast Hot Reload Simulator for HDLs, Haven Skinner, Rafael T. Possignolo, Sheng-Hong Wang, and Jose Renau. IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), April 2020

-

LGraph: A Unified Data Model and API for Productive Open-Source Hardware Design, Sheng-Hong Wang, Rafael T. Possignolo, Qian Chen, Rohan Ganpati, and Jose Renau, Second Workshop on Open-Source EDA Technology (WOSET), November 2019.

-

LGraph: A multi-language open-source database for VLSI, Rafael T. Possignolo, Sheng-Hong Wang, Haven Skinner, and Jose Renau. First Workshop on Open-Source EDA Technology (WOSET), November 2018.

LNAST

- LNAST: A Language Neutral Intermediate Representation for Hardware Description Languages, Sheng-Hong Wang, Akash Sridhar, and Jose Renau, Second Workshop on Open-Source EDA Technology (WOSET), 2019.